### Lecture Notes in Computer Science

Edited by G. Goos, J. Hartmanis and J. van Leeuwen

1680

## Springer Berlin

Berlin

Heidelberg

New York

Barcelona

Hong Kong

London

Milan

Paris

Singapore

Tokyo

Dennis Dams Rob Gerth Stefan Leue Mieke Massink (Eds.)

# Theoretical and Practical Aspects of SPIN Model Checking

5th and 6th International SPIN Workshops Trento, Italy, July 5, 1999 Toulouse, France, September 21 and 24, 1999 Proceedings

#### Volume Editors

Dennis Dams

Eindhoven University of Technology, Department of Electrical Engineering and Department of Mathematics and Computer Science 5600 MB Eindhoven, The Netherlands

E-mail: d.r.dams@ele.tue.nl

Rob Gerth

Intel Microprocessor Products Group, Strategic CAD Laboratories 5200 NE Elam Young Parkway, JFT-104 Hillsboro, OR 97124-6497, USA E-mail: robgerth@ichips.intel.com

Stefan Leue

University of Waterloo, Department of Electrical and Computer Engineering Waterloo, Ontario N2L 3G1, Canada

E-mail: sleue@uwaterloo.ca

Mieke Massink C.N.R.-Ist. CNUCE via Santa Maria 36, 56126 Pisa, Italy E-mail: mieke@gongolo.cnuce.cnr.it

Cataloging-in-Publication data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Theoretical and practical aspects of SPIN model checking: 5th and 6th international SPIN workshops, Trento, Italy, July 5, 1999, Toulouse, France, September 21 and 24, 1999; proceedings / Dennis Dams . . . (ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London; Milan; Paris; Singapore; Tokyo: Springer, 1999

(Lecture notes in computer science; Vol. 1680)

ISBN 3-540-66499-8

CR Subject Classification (1998): F.3, D.2.4, D.3.1

ISSN 0302-9743

ISBN 3-540-66499-8 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

© Springer-Verlag Berlin Heidelberg 1999 Printed in Germany

Typesetting: Camera-ready by author SPIN 10704313 06/3142 – 5 4 3 2 1 0

Printed on acid-free paper

#### **Preface**

Increasing the designer's confidence that a piece of software or hardware is compliant with its specification has become a key objective in the design process for software and hardware systems. Many approaches to reaching this goal have been developed, including rigorous specification, formal verification, automated validation, and testing. Finite-state model checking, as it is supported by the explicit-state model checker SPIN, is enjoying a constantly increasing popularity in automated property validation of concurrent, message based systems. SPIN has been in large parts implemented and is being maintained by Gerard Holzmann, and is freely available via ftp from netlib.bell-labs.com or from URL http://cm.bell-labs.com/cm/cs/what/spin/Man/README.html.

The beauty of finite-state model checking lies in the possibility of building "push-button" validation tools. When the state space is finite, the state-space traversal will eventually terminate with a definite verdict on the property that is being validated. Equally helpful is the fact that in case the property is invalidated the model checker will return a counterexample, a feature that greatly facilitates fault identification. On the downside, the time it takes to obtain a verdict may be very long if the state space is large and the type of properties that can be validated is restricted to a logic of rather limited expressiveness. However, looking at the number and type of practical applications it seems that finite-state model checking technology is moving towards becoming engineering practice. This development can largely be attributed to the relative ease of handling and the potential for automation of the validation process which makes this technology accessible to the software designer and even the domain expert.

The SPIN workshop series was initiated by Jean-Charles Grégoire who hosted the first SPIN workshop in October 1995 at INRS Télécommunications in Montréal. Its success led to subsequent SPIN workshops held in New Brunswick (August 1996), Enschede (April 1997) and Paris (November 1998). At a time when the number of formal methods events is increasing, two conferences expressed interest in hosting SPIN workshops in 1999: the Federated Logic Conference (FLoC'99) held in Trento in June/July, and the World Congress on Formal Methods in the Development of Computing Systems (FM'99) held in Toulouse in September. In order to give SPIN-related research an exposure at both events it was decided to organize two SPIN workshops in 1999. However, both events were to focus on different aspects. The 5th International SPIN Workshop on Theoretical Aspects of Model Checking (5thSPIN99) was held on July 5, 1999 as a satellite workshop of FLoC'99, while the 6th International SPIN Workshop on Practical Aspects of Model Checking (6thSPIN99) was held as a user group meeting within FM'99 on September 21 and 24, 1999.

5thSPIN99 featured an invited talk by John Rushby, 6 research paper presentations that were selected out of 12 submitted papers, an overview of SPIN release 3.3.0 by Gerard Holzmann, an invited tutorial by Kousha Etessami, and

a panel discussion. 6th SPIN99 offered a keynote address by Dan Craigen, an invited tutorial by Rob Gerth, 12 research paper presentations that were selected out of 25 submitted papers, and two tool demonstrations. Papers presented at both workshops are included in this volume.

Acknowledgements. The editors of this volume wish to thank all referees for their tremendous help in putting together a strong program for both workshops. Stefan Leue thanks Piotr Tysowski and Mohammad Zulkernine for their support in organizing the paper review process for 6thSPIN99 and for their aid in putting this volume together. Dennis Dams and Mieke Massink are grateful to the FLoC'99 organization, and in particular to Adolfo Villafiorita, for their support. They also wish to thank Bell-Labs and C.N.R.-Ist. CNUCE for their support of the initiative. Rob Gerth and Stefan Leue wish to express their gratitude to Dines Bjørner for initiating the idea of a SPIN workshop during FM'99, and to the FM'99 organizers for hosting the event.

September 1999

Dennis Dams Rob Gerth Stefan Leue Mieke Massink

#### Organization

#### Organization of 5thSPIN99

#### **Program Committee**

Dennis Dams (Eindhoven University, The Netherlands) Mieke Massink (CNR-Ist. CNUCE, Italy) Gerard Holzmann (Bell Laboratories, USA) Ed Brinksma (Univ. of Twente, The Netherlands)

Marco Daniele (ITC-IRST, Italy)

Bengt Jonsson (Uppsala University, Sweden)

#### Local Organization

Adolfo Villafiorita

#### Referees

| R. Alur     | L. Holenderski | M. Nilsson  |

|-------------|----------------|-------------|

| D. Bošnački | B. Jonsson     | A. Nymeyer  |

| D. Dams     | R. Kaivola     | J. Nyström  |

| M. Daniele  | JP. Katoen     | T. Ruys     |

| G. Faconti  | D. Latella     | N. Sidorova |

| M. Geilen   | G. Lenzini     | R. de Vries |

| S. Gnesi    | M. Massink     |             |

#### Organization of 6thSPIN99

#### **Organizers**

Rob Gerth (Intel Corp., USA) Gerard Holzmann (Bell Laboratories, USA) Stefan Leue (University of Waterloo, Canada)

#### Referees

| K. Etessami  | M. Kamel   | P. Tysowski   |

|--------------|------------|---------------|

| R. Gerth     | G. Karjoth | M. Zulkernine |

| JC. Grégoire | S. Leue    |               |

| G. Holzmann  | W. Liu     |               |

#### **Table of Contents**

| Pa  | art I: Selection of Papers Presented at 5thSPIN99                                                                       |     |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----|

| 1.  | Keynote Address                                                                                                         |     |

|     | segrated Formal Verification: Using Model Checking with Automated estraction, Invariant Generation, and Theorem Proving | 1   |

| 2.  | Theory                                                                                                                  |     |

| Ru  | untime Efficient State Compaction in Spin                                                                               | 12  |

| Dia | stributed-Memory Model Checking with SPIN                                                                               | 22  |

|     | rtial Order Reduction in Presence of Rendez-vous Communications with aless Constructs and Weak Fairness                 | 40  |

| Di  | vide, Abstract, and Model-Check                                                                                         | 57  |

| Pa  | art II: Papers Presented at 6thSPIN99                                                                                   |     |

| 1.  | Keynote Address                                                                                                         |     |

| Fo  | rmal Methods Adoption: What's Working, What's Not!                                                                      | 77  |

| 2.  | Methodology                                                                                                             |     |

| Mo  | odel Checking for Managers                                                                                              | 92  |

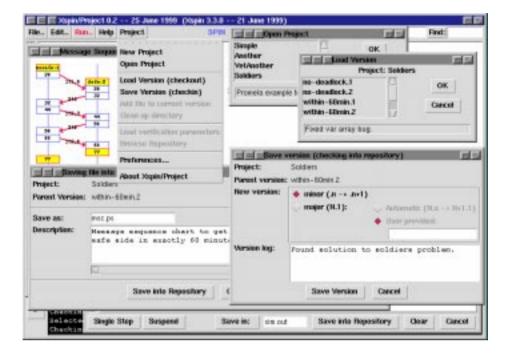

| X   | spin/Project - Integrated Validation Management for Xspin                                                               | 108 |

| 3. Applications I                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

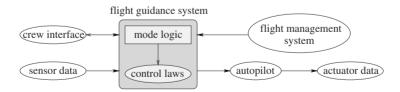

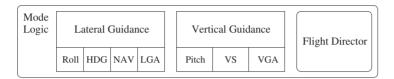

| Analyzing Mode Confusion via Model Checking                                                                                                                 |

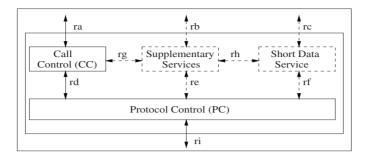

| Detecting Feature Interactions in the Terrestrial Trunked Radio (TETRA)  Network Using Promela and Xspin                                                    |

| JAVA PathFinder, A Translator from Java to Promela                                                                                                          |

| VIP: A Visual Interface for Promela                                                                                                                         |

| 4. Specification and Validation                                                                                                                             |

| Events in Property Patterns                                                                                                                                 |

| Assume-Guarantee Model Checking of Software: A Comparative Case Study 168 Corina S. Păsăreanu, Matthew B. Dwyer, and Michael Huth (Kansas State University) |

| A Framework for Automatic Construction of Abstract Promela Models 184<br>Maria-del-Mar Gallardo, Pedro Merino (University of Malaga)                        |

| 5. Applications II                                                                                                                                          |

| Model Checking Operator Procedures                                                                                                                          |

| Applying Model Checking in Java Verification                                                                                                                |

| 6. Extensions                                                                                                                                               |

| The Engineering of a Model Checker: The Gnu i-Protocol Case Study Revisited                                                                                 |

| Embedding a Dialect of SDL in PROMELA                                                                                                                       |

| dSPIN: A Dynamic Extension of SPIN                                                                                                                          |

| Author Index 277                                                                                                                                            |

# Integrated Formal Verification: Using Model Checking with Automated Abstraction, Invariant Generation, and Theorem Proving\*

John Rushby

Computer Science Laboratory SRI International 333 Ravenswood Avenue Menlo Park, CA 94025, USA rushby@csl.sri.com

**Abstract.** Mechanized formal methods that use both model checking and theorem proving seem to hold most promise for the future. Effective use of both technologies requires they be recast as methods for calculating properties of specifications, rather than merely verifying them. The most valuable properties are those that contribute to the development of invariants and property-preserving abstractions. We outline an architecture for verification tools based on iterated use of such capabilities.

#### 1 Introduction

The advent of model checking not only introduced useful tools, such a SPIN, it also brought a different focus to the field of formal methods. This new focus stressed tools and automated analyses over mathematical derivations performed by hand, and was targeted towards refutation (i.e., finding bugs) more than verification. Many of those who worked on traditional formal verification tools (those based on theorem proving) welcomed the new interest in pragmatics and the sanction that it provided for use of more effective methods of deduction, such as decision procedures. (Formerly, decision procedures had been spurned in some quarters because mechanized verification had—mistakenly, in my view—been identified with the activity of proof in mathematics, rather than with calculation in engineering.)

Some verification tools were extended to incorporate model checking by making a model checker available as a back-end proof procedure—in PVS, for example, a model checker (due to Geert Janssen) is used as a decision procedure for Park's  $\mu$ -calculus restricted to finite types, and CTL model checking is implemented as a derived proof procedure on top of that [14]. Conversely, some

<sup>\*</sup> This research was supported by DARPA through USAF Rome Laboratory Contract F30602-96-C-0204, and by the National Science Foundation contract CCR-9509931.

D. Dams, R. Gerth, S. Leue, M. Massink (Eds.), SPIN'99, LNCS 1680, pp. 1-11, 1999.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 1999

developers of model checkers provided lightweight theorem proving as a front end to overcome limitations in plain model checking [13].

Most users and developers of theorem proving and model checking tools now accept that both technologies are needed, but each tends to see the "other" technology as a supporting player, relegated to the role of a front- or back-end adjunct to their primary tool. In contrast, I believe that significant further advances will be made only by "symmetrically" integrated verification environments in which theorem proving and model checking are seen as equal partners and are used in an iterative, interleaved fashion to provide capabilities such as abstraction and invariant generation, as much as to perform direct verification.

A couple of projects have started to explore the development and use of these symmetric approaches; they include SAL (Symbolic Analysis Laboratory) at SRI and Stanford (with substantial input from Berkeley), and VeriTech at The Technion. In the remainder of this short paper, I will sketch the architectures employed in these systems and some of the techniques used. The systems themselves are still inchoate, and their utility has not yet been demonstrated, so the approach they embody should be regarded as somewhat speculative at present.

#### 2 Common Intermediate Languages

Mechanized formal analysis starts from a description of the problem of interest expressed in the notation of the tool to be employed. Construction of this description often entails considerable work: first to recast the system specification from its native expression in C, Esterel, Java, SCR, UML, Verilog, or whatever, into the notation of the tool concerned, then to extract the part that is relevant to the analysis at hand (the order of these two steps can be reversed), and finally to reduce it to a form that the tool can handle (e.g., finite state). If a second tool is to be employed for a different analysis, then a second description of the problem must be prepared, with considerable duplication of effort. Notice that only the final analysis is automated: the translation, extraction, and reduction steps are all performed by hand (an exception is the Java PathFinder [9] which provides model checking for Java via an automated translation into Promela, the language of SPIN). The reasons for this lack of automation seem economic rather than technical: with m source languages and n tools, we would need  $m \times n$ translators, either m or n "extractors," and n "reducers." This situation naturally suggests use of a common intermediate language, where the numbers of tools required could be reduced to m+n translators and perhaps as few as one extractor and one reducer.

Successful use of an intermediate language seems more promising in this domain than in programming (where the failure of the UNCOL project in the 1960s is still remembered) because we are interested primarily in concurrency issues, where transition relations already provide a widely-accepted semantic foundation.

A useful intermediate language cannot provide just bare transition relations, however, for we will want to support various transformations and analyses on the intermediate representation and these will be inefficient or ineffective if too much of the structure and "intent" of the original specification is lost by flattening it out into a plain transition relation. For these reasons, the SAL intermediate language provides both synchronous and asynchronous forms of composition; distinguishes input, local, and output variables; provides state update via both singlevariable assignments (a style often used for hardware specification) and guarded commands (where several state variables may be updated simultaneously—a style often used in protocol specification), and a module structure. Because SAL is an environment where theorem proving as well as model checking is available, absence of causal loops in synchronous systems is ensured by generating proof obligations, rather than by more restrictive syntactic methods. For example, the following pair of assignments is acceptable in SAL because we can prove that X is causally dependent on Y only when A is true, and vice-versa only when it is false—hence there is no causal loop.

```

X = IF A THEN NOT Y ELSE C ENDIF

Y = IF A THEN B ELSE X ENDIF

```

While there are as yet no automated translators into the SAL language (we hope others will write those if the rest of the system proves effective), we do have translators from SAL to SMV (for model checking), to PVS (for theorem proving), and to Java (for animation).

#### 3 Syntactic Transformations

A number of generally-useful transformations can be defined on systems specified in an intermediate representation. A canonical "extractor" could perform backward slicing on variables to yield just that part of a large system specification that is relevant to a given property [7]. We suspect that many of the complexities of program slicing (e.g., interprocedural data flow and global variables) are much reduced when this technology is applied to specifications rather than imperative programs. (Conversely, we believe that effective automated theorem proving could improve the precision of classical program slicing.)

Other transformations could perform syntactic "reductions" on the state space of a specification. These may, but do not always need to be, property-preserving. For example, a reduction commonly employed in model checking arbitrarily reduces the size of large or infinite data types to small concrete values: the maximum number of messages in a queue may be reduced from n to 3, for instance. Such downscaling may preserve neither soundness (model checking the downscaled instance may fail to reveal bugs in the original) nor completeness (bugs may be found in the downscaled instance that are not present in the original), but can nonetheless be effective in exposing real bugs quite cheaply.

Yet other reductions may be property-preserving: examples may include some defined by abstract interpretation and those associated with partial order reductions. One of the attractions of an intermediate representation is that it may

make techniques such as partial order reduction, presently provided only by SPIN, more widely available.

#### 4 Semantic Transformations

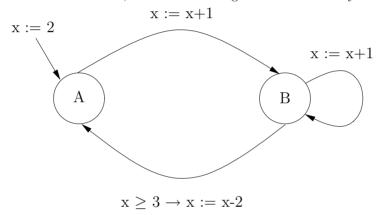

The real power of integrated verification environments only becomes apparent when we consider transformations whose own construction or justification exploits the model checking or deductive capabilities available in the environment. Property-preserving abstractions are the main transformations of this kind. The utility of such abstractions in model checking is well known [5,12], and the topic of interest is how to develop useful abstractions by largely automatic means. To illustrate some of the issues, I use the following trivial transition system.

This system is truly trivial, in that it does not involve concurrency; it features two control locations, A and B, and a single integer-valued state variable x, which can be incremented by one when control is at either location, and decremented by two when control is at B and x is at least three. Initially, control is at A and B has the value two; the goal is to show that B is at least two whenever control is at B.

This system cannot be model checked directly because it is not finite-state (its state variable x can grow arbitrarily large). We could downscale the system by restricting x to some arbitrary minimum and maximum values—say zero and five, respectively—but then we will have to modify the description to do something other than increment when x is at its maximum value, and to do something other than decrement if this would take it below its minimum value, and then we may wonder about the relationship between the original and the downscaled system descriptions, and the interpretation of any results obtained by model checking.

If we wish to draw conclusions about the original system on the basis of model checking a reduced system, then we must ensure that the reduced system is a property-preserving abstraction of the original. Before doing this, however, I wish to set the stage for combined approaches by illustrating how properties of infinite-state systems can be established by theorem proving.

Theorem proving can be used to establish an invariant property (implicitly, those are the only kind of properties considered here) by showing that the property is true in the initial system state and that it is preserved by all transitions of the system. If we feed our example into PVS [15], it quickly discharges three of the four proof obligations and terminates with the following unproven subgoal.

```

[-1] pc(pre!1) = A

[-2] pc(post!1) = B

[-3] x(pre!1) = 0

|------

[1] x(pre!1) + 1 \geq 2

```

PVS displays proof goals in this "sequent" form; the interpretation is that the conjunction of the formulas above the line should imply the disjunction of formulas (here there is only one) below the line. An expression such as pc(pre!1) = A is interpreted as asserting that the control location (or "program counter," hence the abreviation pc) in state pre!1 is A (the !1 suffix is added to ensure that Skolem constants have unique names). This particular sequent is inviting us to consider the case of a transition from A to B, where the value of x is initially zero. Plainly, the invariant is not satisfied in this case (hence the unprovable formula below the line, which reduces to 1 > 2). From our understanding of the system, however, we can see that this case cannot arise, because x must be at least one when control is at A. In order to convince the prover of this, however, we must add it to the invariant as an additional fact to be proven: the invariant is said to be strengthened by adding the extra conjunct. In general, the process of establishing an invariant by theorem proving involves inspecting failed subgoals to deduce plausible additional conjuncts, strengthening the invariant by adding these conjuncts, and repeating the process until the proof succeeds. In one example of this kind, 57 such strengthenings were required to verify a bounded retransmission communications protocol [10]; each conjunct was discovered by inspecting a failed proof, and the process consumed several weeks.

A more integrated approach to this problem is one that uses theorem proving to justify a property-preserving finite state abstraction of the system, and then model checks the abstraction. Given a concrete state space with transition relation  $\mathtt{tr}_c$  and initial states and desired invariant characterized by predicates  $\mathtt{init}_c$  and  $\mathtt{p}_c$ , respectively, we need to find a (finite) abstract state space with an abstraction function  $\mathtt{abs}$  from concrete states to abstract ones, together with an abstract transition relation  $\mathtt{tr}_a$  and predicates  $\mathtt{init}_a$  and  $\mathtt{p}_a$  on the abstract states, such that the following verification conditions hold.

```

1. init_c(cs) \supset init_a(abs(cs)),

2. tr_c(pre_c, post_c) \supset tr_a(abs(pre_c), abs(post_c)), and

3. p_a(abs(cs)) \supset p_c(cs)

```

where cs,  $pre_c$ , and  $post_c$  are concrete states, formulas are implicitly universally quantified over their free variables, and  $\supset$  indicates logical (material) implication. Then we will have

```

invariant(p_a)(init_a, tr_a) \supset invariant(p_c)(init_c, tr_c),

```

and the antecedent can be established by model checking.

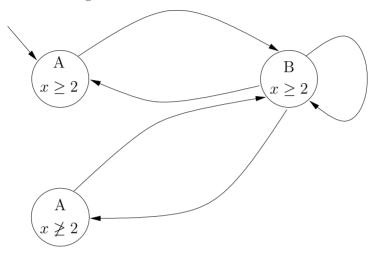

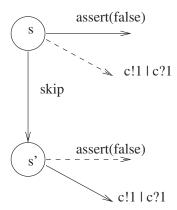

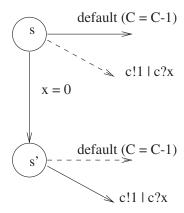

A particularly useful form of abstraction uses a collection of boolean variables to define the abstract state space, where each variable abstracts some predicate over the concrete state space [17]. This is called *predicate abstraction* (or sometimes *Boolean abstraction*) and we can apply it to our example by using just a single abstract variable that abstracts the predicate  $x \geq 2$ . Using insight, we can postulate the following as a suitable transition relation under this abstraction.

We can see by inspection that the desired invariant is satisfied in this system, so it remains to show that the postulated transition relation is a true abstraction of the original. The first and third of the verification conditions listed previously are discharged trivially by PVS, but the second yields the following sequent.

```

[-1] pc(post<sub>c</sub>!1) = B

[-2] x(pre<sub>c</sub>!1) = 0

|------

[1] x(pre<sub>c</sub>!1) + 1 \ge 2

```

Similar to the subgoal that arose in the invariance proof, this is inviting us to consider the case of a concrete transition into B from a state in which  $\mathbf x$  is zero. Also similar to the original invariance proof, we see that this troublesome case can be eliminated by using the fact that  $\mathbf x \geq 1$  is a global invariant of the concrete system—but then we will again need to establish that this is indeed an invariant. As this example illustrates, justification of abstractions generally requires invariants. For the bounded retransmission protocol mentioned earlier, 45 invariants were needed to justify a proposed finite-state abstraction.

Now static analysis can easily establish that  $x \ge 1$  is an invariant of our example system, so one way to enrich an integrated verification environment is by adding a static analysis component (e.g., [4]) that can deduce useful invariants. Justification of a given abstraction can then make use of such known invariants.

The alternative to justifying a given abstraction a posteriori is to construct one that is sound a priori: that is, the construction technique ensures that if the

abstracted property is true of the abstraction so constructed, then the original property is true of the original system (the converse may not be so, however).

Several methods have been proposed for constructing abstracted transition relations for a given abstraction function. One way starts with the universal relation on the abstracted states; then, for each pair of abstract states, generates the verification condition that asserts that the arc between those two states can be removed (the condition is that there is no transition between any pair of original states that map to those abstract states). If the verification condition can be proved (using automatic proof procedures), then the transition can be omitted from the abstracted system description; if not, then it is conservative to include it. [2]. An alternative approach (specialized for predicate abstraction) develops the abstract transition relation by a forward reachability analysis; at each point it generates the verification conditions that lead to successor states with each given predicate true and with it false [18]. Both approaches can generate an abstracted specification for the bounded retransmission protocol in minutes; the first approach (which is implemented in an extension to PVS called InVeSt [3]) has the advantage that it preserves the structure of the original system description, the second (which is implemented in PVS itself) does not preserve structure but is generally faster and develops abstracted systems with fewer states.

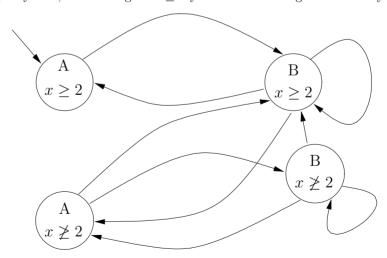

Both these methods require the user to propose the abstraction function (and both work better when supplied with a collection of known invariants). For the case of predicate abstraction, it is natural to start by abstracting on subexpressions of the desired invariant that involve nonfinite variables. With our example system, abstracting on  $x \ge 2$  yields the following abstracted system.

Unfortunately, we see that the abstracted invariant is not satisfied in this system (i.e., the state at the lower right is reachable). If, however, we take a counterexample trace generated by model checking the abstracted system—for example

$$\{\mathtt{A,}\ x\geq 2\}\ \to\ \{\mathtt{B,}\ x\geq 2\}\ \to\ \{\mathtt{A,}\ x\not\geq 2\}\ \to\ \{\mathtt{B,}\ x\not\geq 2\}$$

and then *concretize* it <sup>1</sup>, we will obtain a trace such as

$$\{A, 2\} \rightarrow \{B, 3\} \rightarrow \{A, 1\} \rightarrow ?$$

in which it is impossible to find a final state that both concretizes the final abstract state and satisfies the concrete transition relation. This suggests that our initial abstraction is too coarse and that we should abstract on some additional predicates. Often, those appearing in guards are plausible candidates, but that is not the case here; however, inspection of the counterexample trace suggests  $x \geq 1$  as a candidate. Abstracting on both  $x \geq 2$  and  $x \geq 1$  is a correct solution: it generates the same abstracted system that we previously generated by hand and sought to justify.

Using the abstractor built in to PVS version 2.3, this example is dispatched by a single proof strategy that combines abstraction and model checking when instructed to abstract on both  $x \ge 2$  and  $x \ge 1$ .

A difficulty in all these approaches involving abstraction is that the user must propose an abstraction function (or, equivalently, a set of predicates to be abstracted) that is strong enough to solve the entire problem: this is a substantial challenge that requires considerable insight or experimentation. A variant approach does not seek to construct an abstraction that directly preserves the property of interest: instead, this approach uses theorem proving as its top-level technique, and employs abstraction and model checking to help discharge the subgoals that are generated [16]. The attraction here is that theorem proving will have performed some case analysis in generating the subgoals, so that they will be simpler than the original problem. Therefore the abstraction needed to help discharge a given subgoal can be much simpler than one that discharges the whole problem; furthermore the predicates that appear in the formulas of the subgoal provide useful hints for the construction of a suitable abstraction. Another benefit from developing the abstractions in the context established by a theorem prover is that the prover keeps track of all outstanding proof obligations and subgoals, so that none can be forgotten or overlooked.

The techniques sketched in this section make fairly substantial use of both theorem proving and model checking, but they are still not truly integrated in

<sup>&</sup>lt;sup>1</sup> "Concretization" is the inverse of abstraction; the inverse of the abstraction function is not a function, in general, so some approximation is required.

that model checking is used only to verify the final abstraction (though I did suggest how a counterexample trace could be used to aid diagnosis of an inadequate abstraction). The reason for this is that a traditional model checker returns very little information that can be used in subsequent analyses (basically, true/false plus possibly a counterexample in the latter case). However, it typically will have calculated a great deal of interesting information during its internal computation, and then thrown it away. For example, a symbolic model checker operating in the "forwards" mode calculates<sup>2</sup> the reachable states of its model. Now, the reachable states characterize the strongest invariant of a system, so a concretization of the reachable states of an abstracted system is certainly an invariant, and possibly a strong one, for the original system. This suggests a new way to calculate invariants that may help in the construction of abstracted system descriptions: construct some simpler abstraction (one for which already known invariants are adequate for its construction), and use a concretization of its reachable states as a new invariant that can help construct further abstractions. A practical difficulty in this approach is that the reachable state set calculated by a model checker is not usually made available externally and, in any case, it is usually represented by a data structure (a BDD) that is not directly suitable for input to a theorem prover. This difficulty has been overcome in the CMU version of the SMV model checker, where a print function, implemented by Sergey Berezin, provides external access to the reachable states.

An integrated combination of abstraction and reachability analysis similar to that sketched above is described in a recent paper by Abdulla et al [1]. Another related approach is described by Das, Dill, and Park [6].

#### 5 Conclusion

A significant advance in the effectiveness and automation of verification for concurrent systems seems possible by combining techniques from model checking and theorem proving in a truly integrated environment. A key idea is to change the perception (and implementation) of model checkers and theorem provers from tools that perform verifications to ones that calculate *properties* (such as abstractions and invariants). By iterating through several such tools (together with tools for static analysis) operating on a common intermediate representation, it becomes possible to incrementally accumulate properties (e.g., invariants) that eventually enable computation of a substantial new property (e.g., an abstraction)—which in turn enables accumulation of further properties. By exploiting the combined power of several forms of mechanized formal analysis, proofs and refutations that currently require significant human effort (either in guiding a theorem prover or in constructing clever abstractions) will, I believe, soon become routine calculations.

<sup>&</sup>lt;sup>2</sup> Or can calculate—it may terminate early if it discovers a reachable state that falsifies the desired property.

#### Acknowledgments

None of the work described here is mine; I have drawn freely on the research and insights of my colleagues Saddek Bensalem, David Dill, César Muñoz, Sam Owre, Vlad Rusu, Hassen Saïdi, N. Shankar, Eli Singerman, and Yassine Lakhnech. The SAL project is led at SRI by N. Shankar, and at Stanford by David Dill, and has benefitted from collaboration with Tom Henzinger at UC Berkeley.

I am grateful also to Dennis Dams and Mieke Massink for inviting me to the Fifth Spin Workshop, and for their careful reading of the first version of this paper.

#### References

- Parosh Aziz Abdulla, Aurore Annichini, Saddek Bensalem, Ahmed Bouajjani, Peter Habermehl, and Yassine Lakhnech. Verification of infinite-state systems by combining abstraction and reachability analysis. In Halbwachs and Peled [8], pages 146–159.

- Saddek Bensalem, Yassine Lakhnech, and Sam Owre. Computing abstractions of infinite state systems compositionally and automatically. In Hu and Vardi [11], pages 319–331.

- 3. Saddek Bensalem, Yassine Lakhnech, and Sam Owre. InVeSt: A tool for the verification of invariants. In Hu and Vardi [11], pages 505–510.

- 4. Saddek Bensalem, Yassine Lakhnech, and Hassen Saïdi. Powerful techniques for the automatic generation of invariants. In Rajeev Alur and Thomas A. Henzinger, editors, Computer-Aided Verification, CAV '96, volume 1102 of Lecture Notes in Computer Science, pages 323–335, New Brunswick, NJ, July/August 1996. Springer-Verlag.

- Edmund M. Clarke, Orna Grumberg, and David E. Long. Model checking and abstraction. ACM Transactions on Programming Languages and Systems, 16(5):1512–1542, September 1994.

- Satyaki Das, David L. Dill, and Seungjoon Park. Experience with predicate abstraction. In Halbwachs and Peled [8].

- Matthew B. Dwyer and John Hatcliff. Slicing software for model construction. In Proceedings of ACM SIGPLAN Workshop on Partial Evaluation and Semantics-Based Program Manipulation (PEPM'99), January 1999.

- 8. Nicolas Halbwachs and Doron Peled, editors. *Computer-Aided Verification, CAV* '99, number 1633 in Lecture Notes in Computer Science, Trento, Italy, July 1999. Springer-Verlag.

- 9. Klaus Havelund and Thomas Pressburger. Model checking Java programs using Java PathFinder. Software Tools for Technology Transfer, 1999. To appear.

- Klaus Havelund and N. Shankar. Experiments in theorem proving and model checking for protocol verification. In *Formal Methods Europe FME '96*, volume 1051 of *Lecture Notes in Computer Science*, pages 662–681, Oxford, UK, March 1996. Springer-Verlag.

- Alan J. Hu and Moshe Y. Vardi, editors. Computer-Aided Verification, CAV '98, volume 1427 of Lecture Notes in Computer Science, Vancouver, Canada, June 1998. Springer-Verlag.

- 12. C. Loiseaux, S. Graf, J. Sifakis, A. Bouajjani, and S. Bensalem. Property preserving abstractions for the verification of concurrent systems. *Formal Methods in System Design*, 6:11–44, 1995.

- 13. Ken McMillan. Minimalist proof assistants: Interactions of technology and methodology in formal system level verification. In Ganesh Gopalakrishnan and Phillip Windley, editors, Formal Methods in Computer-Aided Design (FMCAD '98), volume 1522 of Lecture Notes in Computer Science, Palo Alto, CA, November 1998. Springer-Verlag. Invited presentation—no paper in proceedings, but slides available at http://www-cad.eecs.berkeley.edu/~kenmcmil/.

- 14. S. Rajan, N. Shankar, and M.K. Srivas. An integration of model-checking with automated proof checking. In Pierre Wolper, editor, Computer-Aided Verification, CAV '95, volume 939 of Lecture Notes in Computer Science, pages 84–97, Liege, Belgium, June 1995. Springer-Verlag.

- 15. John Rushby, Sam Owre, and N. Shankar. Subtypes for specifications: Predicate subtyping in PVS. *IEEE Transactions on Software Engineering*, 24(9):709–720, September 1998.

- 16. Vlad Rusu and Eli Singerman. On proving safety properties by integrating static analysis, theorem proving and abstraction. In W. Rance Cleaveland, editor, *Tools and Algorithms for the Construction and Analysis of Systems (TACAS '99)*, volume 1579 of *Lecture Notes in Computer Science*, pages 178–192, Amsterdam, The Netherlands, March 1999. Springer-Verlag.

- 17. Hassen Saïdi and Susanne Graf. Construction of abstract state graphs with PVS. In Orna Grumberg, editor, Computer-Aided Verification, CAV '97, volume 1254 of Lecture Notes in Computer Science, pages 72–83, Haifa, Israel, June 1997. Springer-Verlag.

- 18. Hassen Saïdi and N. Shankar. Abstract and model check while you prove. In Halbwachs and Peled [8], pages 443–454.

#### Runtime Efficient State Compaction in Spin

J Geldenhuys and PJA de Villiers

Department of Computer Science, University of Stellenbosch, 7600 Stellenbosch, SOUTH AFRICA {jaco,pja}@cs.sun.ac.za

Abstract. Spin is a verification system that can detect errors automatically by exploring the reachable state space of a system. The efficiency of verifiers like Spin depends crucially on the technique used for the representation of states. A number of recent proposals for more compact representations reduce the memory requirements, but cause a considerable increase in execution time. These methods could be used as alternatives when the standard state representation exhausts the memory, but this is exactly when the additional overhead is least affordable.

We describe a simple but effective state representation scheme that can be used in conjunction with Spin's normal modes of operation. We compare the idea to Spin's standard state representation and describe how Spin was modified to support it. Experimental results show that the technique provides a valuable reduction in memory requirements and simultaneously reduce the execution time. For the cases considered an average reduction in memory requirements of 40% was measured and execution time was reduced on average by 19%. The proposed technique could therefore be considered to replace the default technique in Spin.

#### 1 Introduction

Model checking has been applied successfully to detect errors in systems of realistic size and complexity [1,6]. Spin is a well-known model checker that does on-the-fly state exploration to verify correctness claims stated as temporal logic formulae. With model checkers such as Spin there are two main concerns: (1) the efficiency of state generation and (2) the amount of memory needed to store unique states. The state generation algorithm used in Spin is highly efficient, but it seems possible to improve state storage.

Currently, SPIN must be used in *supertrace mode* to cope with large state spaces. This involves using a controlled partial search. The technique is based on hashing without collision detection and when collisions do occur, search paths are sometimes terminated prematurely. Unfortunately this means that errors could be missed.

A full state space exploration is always preferable, but this is only possible for much smaller models because all unique states must be stored in memory. One remedy is to reduce the state size by storing states in compacted form. Various state compaction techniques have been investigated, but all increase the execution time significantly [3, 5, 7]. In this paper we describe a state representation

technique that is simple to implement. It does not only reduce the memory requirements, but often reduces the execution time as well. Section 2 describes the principles underlying our technique and Section 3 explains how the SPIN source code was modified to incorporate the proposed technique; results are presented in Section 4.

#### 2 Proposed State Representation Technique

The global state of a Promela model consists of the values of the variables in all processes. Usually each state includes several data variables and a single location variable per process. These variables are aligned on byte boundaries because Promela supports various 8-bit, 16-bit and 32-bit types. Because one or more bytes are allocated to each variable, state sizes of more than a hundred bytes are not exceptional. Therefore, if all unique states are stored explicitly in uncompacted form, a model that generates a few million states quickly exhausts the memory available on typical workstations.

Most variables in validation models only assume a small subset of their potential values. An efficient technique to map these values onto consecutive integers would save a substantial amount of memory. One possible strategy is to enter unique states as they are encountered in lookup tables. This is the principle behind the approaches in [5, 7]. The position (index) in the table where a given state is entered then serves to identify the much larger state value. However, the overhead of manipulating these tables increases the execution time.

A significant reduction in state size is possible by simply placing tighter bounds on the ranges of variables and packing them into the minimum space required. This idea is the essence of the technique proposed here. Users can easily supply the information about the ranges of variables if the validation language supports user-definable types. For example, type definitions such as "ProcNumber = 0...4" are easy to use and provide enough information to store variables in compacted form.

A small example will illustrate the basic idea. Assume that a model contains three variables  $v_1$ ,  $v_2$ , and  $v_3$  which can respectively assume values from the ranges 0...4, 0...2, and 0...6. Reflecting the number of different values each variable can assume, the compacted form V of each given state is computed as

$$V = v_3 + 7(v_2 + 3v_1)$$

=  $v_3 + 7v_2 + 7 \cdot 3v_1$

Two constant factors are associated with each variable  $v_i$ . These factors, known as the lower and upper factors of each variable, are denoted by  $v_i^l$  and  $v_i^u$  respectively. In the example above,  $v_3^l=1$ ,  $v_3^u=7$ ,  $v_2^l=7$ ,  $v_2^u=7\cdot 3=21$ ,  $v_1^l=21$ , and  $v_1^u=7\cdot 3\cdot 5=105$ . These factors are used as masks to extract and update the value of a specific variable in the compacted representation of a state.

Variables are manipulated by two basic operations which must be implemented as efficiently as possible. The operation GetValue used to extract the

value of a given variable  $v_i$  from a compacted state V is simple:  $v_i = (V \mod v_i^u) div \ v_i^l$ . A simple adjustment is necessary to accommodate variables with non-zero offsets. The operation SetValue, which is used to change the value of a variable  $v_i$  to  $v_i'$ , is a little more complex. The new compacted state V' is given by  $V' = V + v_i^l \cdot (v_i' - v_i)$ . The operations GetValue and SetValue represent the only overhead at execution time.

Assume that the number of values allowed for variable  $v_i$  is denoted by  $|v_i|$  and that the lower and upper factors associated with  $v_i$  are denoted by  $v_i^l$  and  $v_i^u$ , respectively. The lower factor of variable  $v_1$  is 1 and its upper factor is  $|v_1|$ . For i > 1 the lower and upper factors of variable  $v_i$  are given by

$$v_i^l = v_{i-1}^u$$

$$v_i^u = |v_i| \cdot v_i^l$$

These constants are computed only once for each variable and therefore contribute only a small constant overhead to the validation run. The number of bits required to store a compacted state with n variables is

$$\lceil \log_2 \prod_{i=1}^n |v_i| \rceil$$

For instance, the number of bits required to store  $v_1$ ,  $v_2$ , and  $v_3$  in the example above is  $\lceil \log_2 5 \cdot 3 \cdot 7 \rceil = 7$ .

#### 3 Experimental Implementation Using Spin

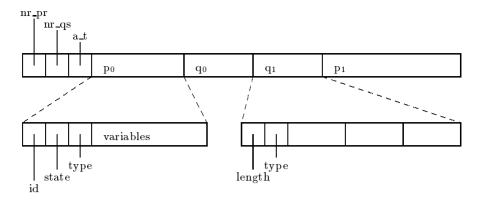

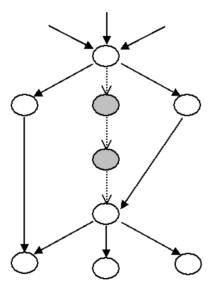

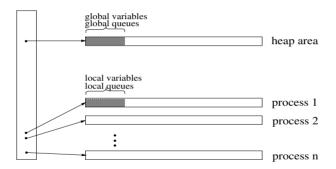

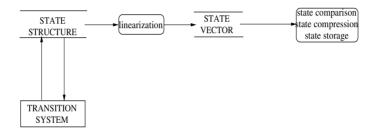

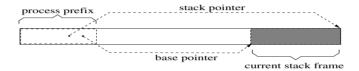

A detailed description of SPIN can be found in [4]. Most relevant here, is the format of the state vector as shown in Figure 1. The state vector stores the current state. It contains the number of processes  $(nr_pr)$ , the number of queues  $(nr_qs)$ , flags for cycle detection  $(a_t)$  and the contents of processes and queues. Each process (such as  $p_0$ ) contains a unique identifier, its local state, the process type, and the values of its local variables. Each queue (such as  $q_1$ ) contains the queue length, queue type, and the values of its elements. Unused elements are stored as zeros. The state vector is continually referenced as the values of variables are read and modified. It is kept in uncompacted form to speed up references to variables.

The SPIN verifier explores the state space in a depth-first manner, storing only the current execution path in a stack. The amount of memory required by the stack is not a serious concern; although the stack may sometimes contain several thousands of states, it is usually small relative to the size of the state space. A more serious problem is that in full search mode all unique states must be stored in a state table. In practice, the number of states that can be stored in the table determines the maximum size of models that can be handled. This is where compaction pays off: it makes it possible to store more states in the same amount of memory.

Fig. 1. Standard form of the state vector

It is not practical to store the entire compacted state as a single number and therefore variables are packed into subgroups called *cells*. Each cell is compacted separately and variables may not be split over more than one cell. This causes a small amount of space wastage, but speeds up the manipulation of variables. In the experimental implementation the state vector consists of an array of cells of type unsigned long. Each variable in the model is given a unique number, called its *position*. There are three tables: cell\_number maps each position to the cell where it is stored, lower\_factor maps each position to its lower factor, and upper\_factor maps each position to its upper factor. The compacted state vector is stored in a global array variable called sv. The implementations of the SetValue and GetValue operations are simple:

```

void SetValue(int pos, int delta)

{

sv[cell_number[pos]] += lower_factor[pos] * delta;

}

int GetValue(int pos)

{

return sv[cell_number[pos]] %

upper_factor[pos] / lower_factor[pos];

}

```

The pos parameter refers to the position of a variable, and the delta parameter of SetValue is the value  $(v'_i - v_i)$ , the difference between the old and new values of the variable.

However, this implementation of GetValue is too slow. A simple remedy is to keep an uncompacted copy of the current state in variable usv. For most models, the size of usv is less than 1 Kbyte. It is unnecessary to store usv in the state table, but, unfortunately, it must be stored on the stack to allow the

current implementation of SPIN to backtrack more than one state at a time. The following more efficient implementations of SetValue and GetValue were therefore used:

```

void SetValue(int pos, int delta)

{

sv[cell_number[pos]] += lower_factor[pos] * delta;

usv[pos] += delta;

}

int GetValue(int pos)

{

return usv[pos];

}

```

As new variables are created during the execution of a model, they are added to the state vector. This task is performed by the AddPosition routine. The parameter card indicates the cardinality  $(|v_i|)$  of the new variable.

```

void AddPosition(int card)

{

if (MAXCELLVALUE / upper_factor[maxpos - 1] <= card)

{

/* use a new cell */

lower_factor[maxpos] = 1;

cell_number[maxpos] = cell_number[maxpos - 1] + 1;

}

else

{

lower_factor[maxpos] = upper_factor[maxpos - 1];

cell_number[maxpos] = cell_number[maxpos - 1];

}

upper_factor[maxpos] = lower_factor[maxpos] * card;

maxpos += 1;

}</pre>

```

The global variable maxpos stores the number of the highest position allocated so far. The test determines whether the new variable will fit into the current cell, or whether a new cell must be used. When a new cell is allocated, the last few bits of the previous cell are sometimes left unused. It is possible to minimize the number of bits wasted by reordering the variables, although this was not attempted in the current implementation.

Currently, a slightly restricted version of Promela is supported:

Different orders of process activation along different execution paths are forbidden.

- No global channels are currently allowed. If necessary, models must be adapted so that the init process contains all channels, passing them to processes when they are created.

- The ranges of variables must start at 0.

It was necessary to make several modifications to the SPIN source code to implement the compaction technique: the PROMELA grammar was extended with a new data type, the translation of PROMELA statements was modified and a few other routines in the SPIN system were adapted to use the new state representation.

#### 3.1 Modifications to the Promela Grammar

The range of each variable is needed and the simplest way to obtain this information is to ask the user to supply it. The PROMELA grammar was therefore extended to allow a new data type: value n. Instead of declaring a variable as

```

byte x;

we write

```

```

value 12 x:

```

which means that variable  $\mathbf{x}$  can take on 12 different values ranging from 0 to 11. The declaration

```

mtype = { A, B, C, D };

```

is transformed into

```

#define A 4

#define B 3

#define C 2

#define D 1

#define mtype value 5

```

(The values for the messages were chosen to be internally consistent with the current Spin implementation.) So, instead of

```

chan q = [4] of { mtype, int };

we could write

chan q = [4] of { mtype, value 6 };

```

In our opinion, it would be better to provide such user-definable types to replace the fixed types of PROMELA. This would allow users to place tighter bounds on the ranges of variables. The notation above was selected for its simplicity; it may be more convenient to also specify the lower bound, to allow types such as " $-2\dots 2$ " and " $60\dots 70$ ". It may also be useful to allow user-defined subrange types instead of the scheme described above. As an example, a counter that can take on values 0 through 10 could then be declared as follows:

```

subrange Counter = 0...10;

Counter c;

```

#### 3.2 Modification to the Manipulation of Variables

Normally Spin translates Promela statements to code that performs operations on the normal state vector shown in Figure 1. This system was modified so that the generated code acts on the new compacted state vector. The most important statements are accesses to local variables of processes.

A read access of variable x is translated as

```

GetValue(pos)

```

where pos is the position of x in the state vector. A write access, or assignment, x = e, is translated as

```

SetValue(pos, e - GetValue(pos))

```

Turning to a more concrete example, consider the Promela statement

```

x = y + 2

```

where x and y are local variables of some process. This is normally translated as

```

case 6: /* STATE 5 - [x = (y+2)] */

IfNotBlocked

(trpt+1)->oval = ((int)((P2 *)this)->x);

((P2 *)this)->x = (((int)((P2 *)this)->y)+2);

m = 3; goto P999;

```

In the modified version of Spin the assignment is translated as

```

case 6: /* STATE 5 - [x = (y+2)] */

IfNotBlocked

pos = curproc+14;

delta = (GetValue(curproc+15) + 2) - GetValue(pos);

(trpt+1)->oval = delta;

SetValue(pos, delta);

m = 3; goto P999;

```

The main difference is that procedures GetValue and SetValue are used to manipulate variables. The constants 14 and 15 in the example are the positions of variables x and y relative to the start of the process to which they are local. The starting position of the variables of a process is stored in curproc.

#### 4 Results

A number of well-known PROMELA models were used to measure the effectiveness of the compaction technique. Some of the models (leader, pftp, snoopy, and sort) are part of the standard Spin distribution, but were slightly modified to adhere

to the restrictions of our implementation. The other models (cambridge and slide) were collected from the Internet<sup>1</sup>.

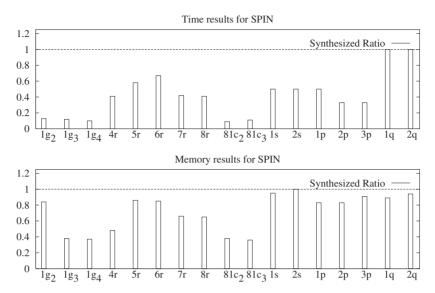

Table 1 shows the memory required (in Mbytes) followed by the time needed to complete each validation run (in seconds)<sup>2</sup>. The first column (marked SPIN) gives the results for the standard SPIN system. The next column (marked SPIN-C) is for the modified SPIN system with compact representation of states. The last column shows the ratio between the two systems for purposes of comparison.

| Table 1. Comparison | $of\ standard$ | $\operatorname{Spin}$ | $\operatorname{against}$ | ${\rm Spin}$ | $\mathbf{wit}\mathbf{h}$ | $_{\rm the}$ | $\operatorname{prop}\operatorname{osed}$ | compression |  |

|---------------------|----------------|-----------------------|--------------------------|--------------|--------------------------|--------------|------------------------------------------|-------------|--|

| technique (Spin-C)  |                |                       |                          |              |                          |              |                                          |             |  |

| Model                                | Spin   |               | Spin-          | $\cdot$ C    | Ratio  |               |

|--------------------------------------|--------|---------------|----------------|--------------|--------|---------------|

|                                      | memory | $_{\rm time}$ | $_{ m memory}$ | $_{ m time}$ | memory | $_{\rm time}$ |

| cambridge                            | 54.1   | 6.9           | 23.8           | 6.8          | 0.44   | 0.99          |

| leader                               | 91.7   | 12.6          | 33.2           | 7.7          | 0.36   | 0.61          |

| $\operatorname{pft}\operatorname{p}$ | 66.6   | 8.9           | 26.5           | 7.3          | 0.40   | 0.83          |

| snoopy                               | 15.2   | 1.7           | 10.6           | 1.4          | 0.70   | 0.84          |

| $\operatorname{sort}$                | 3.7    | 0.3           | 4.4            | 0.2          | 1.19   | 0.77          |

| sort(BIG)                            | 130.7  | 22.6          | 70.4           | 14.7         | 0.54   | 0.65          |

| $\operatorname{slide}$               | 33.3   | 3.2           | 20.3           | 3.2          | 0.61   | 0.97          |

| Average                              |        |               |                | •            | 0.60   | 0.81          |

Note that the technique works best for the larger models. A useful reduction in memory requirements was measured for most models, the average being 40%. More surprising, however, is that execution time was *decreased* on average by 19%.

As can be expected, the results differ from one model to the next. This is due to differences in the number of variables, the number of read and write accesses, and the structure of the state space. In fact, when models use large amounts of stack memory compared to the amount of state table memory, the technique does not seem to help at all.

For example, a model of six dining philosophers<sup>3</sup> yields a memory ratio of 1.89 and a time ratio of 1.11. This model is unusual because the stack reaches a depth of 152383 states, while the state table contains only 94376 states. For the majority of models, the situation is reversed. The execution time is longer in this case, since a substantial overhead is associated with pushing states onto the stack. This overhead comes from copying the uncompacted state vector to the stack. This overhead is avoided in Spin's standard mode of operation because the uncompacted state vector is not stored in the stack. A substantial modification of the internal mechanisms of Spin is required to address this problem, but

<sup>1</sup> http://cm.bell-labs.com/cm/cs/what/spin/Man/Exercises.html

<sup>&</sup>lt;sup>2</sup> Tests were executed on a 400MHz Pentium II with 256 Mbytes of memory.

http://www.ececs.uc.edu/~imutaban/miniproject/2Phase/2phase.html

this was not attempted since our goal was simply to test the feasibility of the technique in the context of SPIN.

More information about the models is given in Table 2. The first three columns give the size of the original SPIN state vector in bytes, the number of variables in each model, and the number of cells (of 4 bytes each) occupied by the compacted state vector. The last two columns contain the number of unique states and length of the longest path on the stack.

| M                     | lodel       | Spin | # variables | cells | states | $\operatorname{depth}$ |

|-----------------------|-------------|------|-------------|-------|--------|------------------------|

| $\operatorname{can}$  | ıbridge     | 64   | 52          | 5     | 728544 | 13004                  |

| lead                  | $_{ m ler}$ | 148  | 223         | 18    | 341290 | 148                    |

| pftp                  | )           | 140  | 109         | 11    | 439895 | 5780                   |

| sno                   | ору         | 196  | 105         | 14    | 91920  | 12250                  |

| $\operatorname{sort}$ |             | 140  | 92          | 16    | 15351  | 115                    |

| $\operatorname{sort}$ | (BIG)       | 188  | 147         | 23    | 659683 | 202                    |

| $\operatorname{slid}$ | e           | 52   | 43          | 4     | 510111 | 51072                  |

Table 2. More details about models

#### 5 Discussion and Conclusions

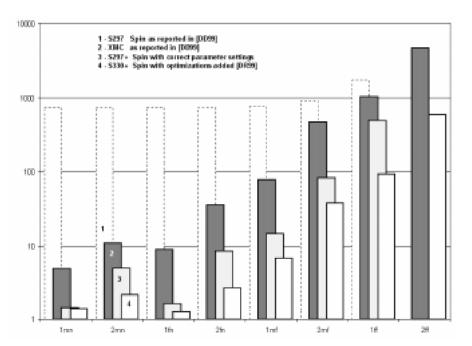

Compact representation of states is crucial in verifiers like SPIN and various compaction techniques have been investigated by modifying the SPIN source code. In Table 3 a comparison is given for five such techniques. (Only the pftp and snoopy data are available for all techniques considered.) The measurements in the table were taken from the literature [3,5,7]. Although they were measured on different platforms and cannot be compared directly to each other, they provide a rough indication of the cost of each technique.

Because the platforms and validation models differ, it is difficult to draw general conclusions about the effectiveness of specific techniques. However, all compression techniques proposed thus far seem to increase execution times while the technique proposed in this article can *reduce* the runtime required. This is surprising. A possible explanation is that the reduction in state size—which speeds up state comparison and manipulation—must be more than enough to compensate for the compression overhead. On the negative side, only a fair amount of compression can be expected in general.

The impressive performance of some compression techniques rely on extra information that must be supplied by users. For example, it may be necessary to obtain information about the behaviour of variables from training runs [3, 5]. In addition, the most powerful technique considered ([3]) requires that users define an encoding for state information. To be fair, this extra time and effort cannot be ignored. The technique proposed here only needs information that can be derived automatically from the declaration of variables at compile time.

0.15

0.18

0.40

2.42

2.54

0.83

0.27

0.70

3.23

$\bar{3}.47$

0.84

| 001 | MHZ Pentium II.            |                |              |        |               |

|-----|----------------------------|----------------|--------------|--------|---------------|

|     | $\operatorname{Technique}$ | pftp           |              | snoop  |               |

|     |                            | $_{ m memory}$ | $_{ m time}$ | memory | $_{\rm time}$ |

|     | GETSs [3]                  | 0.05           | 2.07         | 0.09   | 3.38          |

|     | State compression [7]      | 0.25           | 1.24         | 0.17   | 0.29          |

|     | Recursive indexing [5]     | 0.18           | 1.41         | 0.33   | 2.45          |

Two-phase compression [5]

State compaction (proposed technique)

Recursive indexing [5]

Table 3. Comparison of state compression techniques. The first four rows of measurements were taken directly from the literature, while the last two rows were measured on a 400MHz Pentium II.

The technique relies on extra information regarding the minimum and maximum values assumed by variables. It is easy to obtain this information if user-definable types are used instead of the predefined fixed types of PROMELA. In fact, based on our experience with ESML [2]—a specification language similar to PROMELA—we know that it requires little extra effort of users to define the ranges of variables more precisely. When it comes to the implementation of such models, it is trivial to find the optimal representation for integer subranges.

We have demonstrated the feasibility of our idea in a well-known context by modifying the SPIN source code to test the technique. The results indicate that substantially larger models can be handled in full search mode, while reducing execution time as a bonus.

#### References

- 1. E. M. Clarke and J. M. Wing. Formal methods: state of the art and future directions. ACM Computing Surveys, 28(4):626-643, December 1996.

- 2. P. J. A. de Villiers and W. C. Visser. ESML—a validation language for concurrent systems. South African Computer Journal, 7:59-64, July 1992.

- J.-Ch. Grégoire. State space compression in SPIN with GETSs. In Proceedings of the 2nd SPIN Workshop, 1996.

- 4. G. J. Holzmann. Design and Validation of Computer Protocols. Prentice Hall Software Series, 1991.

- G. J. Holzmann. State compression in SPIN: recursive indexing and compression training runs. In Proceedings of the 3rd SPIN Workshop, 1997.

- J. Rushby. Mechanized formal methods: progress and prospects. In Proceedings

of the 16th Conference on the Foundations of Software Technology and Theoretical Computer Science, Lecture Notes in Computer Science #1180, pages 43-51.

Springer-Verlag, December 1996.

- W. C. Visser. Memory efficient state storage in Spin. In Proceedings of the 2nd SPIN Workshop, 1996.

#### Distributed-Memory Model Checking with SPIN

Flavio Lerda and Riccardo Sisto

Dipartimento di Automatica e Informatica Politecnico di Torino Corso Duca degli Abruzzi, 24, I-10129 Torino (Italy) e-mail: flerda@athena.polito.it, sisto@polito.it

Abstract. The main limiting factor of the model checker SPIN is currently the amount of available physical memory. This paper explores the possibility of exploiting a distributed-memory execution environment, such as a network of workstations interconnected by a standard LAN, to extend the size of the verification problems that can be successfully handled by SPIN. A distributed version of the algorithm used by SPIN to verify safety properties is presented, and its compatibility with the main memory and complexity reduction mechanisms of SPIN is discussed. Finally, some preliminary experimental results are presented.

#### 1 Introduction

The model checker SPIN [4] is a tool widely used to verify concurrent system models. Its success depends on many factors, among which its amazing efficiency in performing model checking and its portability, i.e. the fact that, being written in ANSI C, it runs on most computer platforms.

The main limitation of SPIN, of course shared by all other verification tools based on reachability analysis, is that it can deal with models up to a given maximum size. As a model gets larger and larger, also the memory usage increases, and when the amount of memory used becomes greater than the available physical memory, the workstation is forced to use virtual memory. Since the memory is mainly allocated for a hash table, which is accessed randomly, the system will proceed slowly due to thrashing. In practice, it can be observed with SPIN that when the memory used is less than the physical available memory the performance of the model checker is excellent, and execution time is generally at most in the order of minutes, but as soon as the physical memory is exhausted the performance drops down dramatically. As a consequence, the maximum model size that SPIN can deal with depends essentially on the amount of physical memory that is available.

Various techniques are used by SPIN to reduce the amount of memory needed for verification, thus making the analysis of larger models possible. The main examples are state compression, partial order reductions and bit state hashing. A different technique that could be applied to further extend the size of the verification problems that can be successfully handled by SPIN is the use of a distributed-memory environment such as a network of workstations (NOW),

D. Dams, R. Gerth, S. Leue, M. Massink (Eds.), SPIN'99, LNCS 1680, pp. 22-39, 1999.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 1999

which is ultimately a way to increase the amount of actually available physical memory, and to increase the speed of the verification process by exploiting parallel processing. In this paper we explore this possibility and present some preliminary results. Attention is focused here only on verification of safety properties such as deadlocks and assertions, and not on LTL model checking, which is left for further study.

As memory in SPIN is used mainly to store states, the distributed version of SPIN that we consider is based on a partition of the state space into as many state regions as the number of network nodes. Each node is assigned a different state region, and holds only the states belonging to that subset. In this way, the state table is distributed over a NOW. Each node computes the successors of the states that it holds and, if it finds any successors belonging to other state regions, it sends them to the nodes that are in charge of processing them. Of course, performance depends on how the state space is partitioned, the best results being obtained if the workload is well balanced and communication is minimized. In this paper we consider different possible approaches to the partitioning problem and compare them.

Another important issue that must be taken into consideration is that a distributed version of SPIN should not exclude the use of the other main memory and complexity reduction techniques available in the centralized version, such as state compression, partial order reduction, and bit state hashing. The approach that we consider in this paper is characterized by good compatibility with such mechanisms.

Since one of the strengths of SPIN stands in its portability and widespread use, we decided to develop an experimental distributed version of SPIN that can run on a very common platform: a NOW made up of heterogeneous workstations, interconnected with a standard 10Mbps Ethernet and using the TCP/IP protocol. Of course, more sophisticated communication infrastructures may yield better performance, but the basic environment that we considered is generally available to everyone, and its performance can be considered a reasonable lower bound.

A parallel/distributed version of a reachability analysis model checker, based on the Mur $\varphi$  Verifier [2], was proposed in [8]. The approach taken in [8] is similar to our one, but we use different ways to partition the state space. Moreover, in contrast with SPIN, the Mur $\varphi$  model checker uses a model where the computation of the next states may be quite complex, so with Mur $\varphi$  the most critical resource is not memory, but time. As documented in [8], there are cases where a verification run may take up to several days to complete. For this reason, the main purpose of the distributed version of Mur $\varphi$  is to speed up the verification process, exploiting parallel processing. With our distributed version of SPIN instead we mainly aim at making tractable models that otherwise would be intractable. Moreover, any speed up attained thanks to parallel processing tends to be obscured by communication overhead, which is generally predominant with respect to the short time taken by SPIN in computing the next states.

There has been also a previous proposal to develop a distributed model checker [1], in which the future state computation and the storage function are located at different nodes. This architecture is more complex than our one and the communication overhead is higher because each state is transferred at least two times over the network, since it has to go from the computation node that generated it to the storing node where it is kept for future reference and then back again from it to the computation node that must find its successors.

The rest of the paper is organized as follows. First, the distributed version of the SPIN verification algorithm is described, along with some implementation issues. Then the compatibility of this algorithm with the main memory and complexity reduction mechanisms of SPIN is discussed, and some preliminary experimental results are given. Finally, some conclusions are drawn and perspectives for further research are discussed.

#### 2 The Distributed Verification Algorithm

#### 2.1 The Centralized Algorithm

When SPIN must verify safety properties of a concurrent system, such as proper termination and state properties, it generates a verification program that makes a depth first visit of the system state space graph. The following pseudo code represents the centralized version of such a program:

```

procedure Start(start_state);

begin

V := {}; { already visited states }

DFS(start_state);

end:

procedure DFS(state);

begin

if not state in V then

begin

V := V + state;

for each sequential process P do

nxt = all transitions of P enabled in state

for each t in nxt do

st = successor of state after t

DFS(st);

end:

end;

end;

end:

```

The procedure DFS makes a depth first visit of the graph, and is first called on the initial state (start\_state). If the state to visit is not already present in the set of visited states V, it is added to V, and the DFS procedure is recursively called for each of its possible successors st. The computation of the successors consists of identifying the enabled transitions of the processes making up the model and determining the successor of the current state after each of such transitions. When an already visited state is found, the visit does not proceed any deeper.

For efficiency, the recursive DFS procedure is simulated by means of a user defined stack that contains the moves made from the initial state to the current state, along with all the information needed to restore the current state after a simulated recursive call of DFS(st). The set of visited states V is implemented by an hash table with collision lists, which is generally the most memory consuming data structure, its size being proportional to the number of states in the state graph. Also the stack data structure can consume a considerable amount of memory, because its size is proportional to the depth of the state graph, which, in some cases, can be comparable with the number of states.

#### 2.2 The Distributed Algorithm

The idea at the basis of the distributed version of the verification algorithm is to partition the state space into as many subsets as the number of network nodes. Every node owns one of the state subsets, and is responsible for holding the states it owns and for computing their successors. When a node computes a new state, first it checks if the state belongs to its own state subset or to the subset of another node. If the state is local, the node goes ahead as usual, otherwise a message containing the state is sent to the owner of the state. Received messages are held in a queue and processed in sequence. When all queues are empty and all nodes are idle the verification ends.

The following pseudocode illustrates the algorithm used in the distributed version:

```

procedure Start(i, start_state);

begin

V[i] := {}; { already visited states }

U[i] := {}; { pending queue }

j := Partition(start_state);

if i = j then

begin

U[i] := U[i] + start_state;

end;

Visit(i);

end;

procedure Visit(i);

begin

```

```

while true do

begin

while U[i] = \{\} do

begin

end:

S := extract(U[i]);

DFV(i,S);

end;

end;

procedure DFV(i, state);

begin

if not state in V then

begin

V[i] := V[i] + state:

for each sequential process P do

begin

nxt = all transitions of P enabled in state

for each t in nxt do

begin

st = successor of state after t

j := Partition(st);

if j = i then

begin

DFV(i, st);

end else begin

U[j] := U[j] + st;

end:

end:

end;

end:

end:

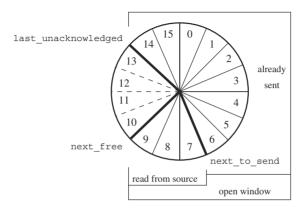

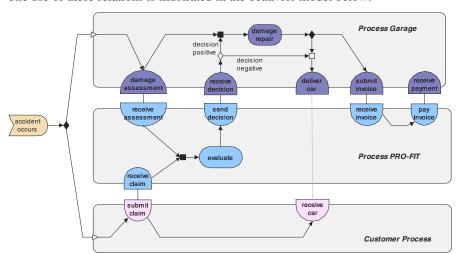

```